本記事では伝送線路シミュレーションに必要不可欠なIBISモデルの基本情報について説明します。

IBISモデルは Input/Output Buffer Information Specificationの略で、プリント基板上の配線を流れる信号波形をシミュレーションするために使うICのモデルです。プリント基板上のIC間の信号を精度良くシミュレーションするためには実際の製品を再現したモデルを用いなければ、正しい結果が得られません。IBISモデルはその名の通り、ICがドライバーとしてどのような出力特性を持つのか、またレシーバとしてどの程度の負荷となるのかなどの情報を記述したモデルになります。

IBISモデルの特徴

SPICEモデルとの違い

ICのモデルとして他に代表的なモデルがSPICEモデルになります。SPICEモデルはトランジスタレベルでモデルを構成できるため、実際のICの動作を忠実に再現することが可能です。それに対して、IBISモデルはICの最終段のIOバッファの部分のみの特性を記述したものになります。

IBISモデルのメリット

IBISモデルのメリットとして、計算の軽さ、情報の秘匿性、取り扱いの簡単さがあります。

- メリット1.計算の軽さ

前述のとおり、SPICEモデルはトランジスタレベルでモデル化し、そのトランジスタの特性を正確に再現するために多数の半導体パラメータで複雑な計算を行います。また、トランジスタレベルでの構成となるため、素子数も多く、回路規模が大きくなるためシミュレーションする際の計算量が多くなり、解析時間が長くなってしまいます。

それに対してIBISモデルはIOバッファの特性のみを再現するため、計算量が小さく、解析時間がSPICEに比べて短いというメリットがあります。

- メリット2.情報の秘匿性

二つ目のメリットの情報の秘匿性についてですが、SPICEモデルはトランジスタレベルのモデルなので、半導体プロセスの情報に関わるパラメータが必要になります。そのような情報は基本的には機密事項なので、モデルの暗号化や機密保持契約などを行った上でモデルのやりとりを行う必要があります。

それに対してIBISモデルはIOバッファの特性のみをテキスト形式で記述しているだけでなので、前述のような機密となる情報は含んでおりません。従って、ICベンダーとしてはモデルを公開しやすく、WEB上からダウンロードできるなど、ユーザーにとっても入手が容易なモデルになります。

- メリット3.取り扱いの簡単さ

IBISモデルはIBIS open forumでの規格に則って記述されるため、モデル毎に取り扱いが一様であるというメリットがあります。SPICEモデルはモデル毎に全く異なる入出力ピンや設定情報を持つため、モデル毎のセットアップが必要ですが、IBISモデルは入出力ピンや設定方法含めて規格化されているため、ベンダーの異なるモデルであっても同様の取り扱いが可能です。

IBISモデルのデメリット

SPICEモデルと比べた時のIBISモデルのデメリットとして、特に下記の点について、考慮することができない事に注意する必要があります。下記のケースを考慮しなくてよい場合には、基本的にSPICEモデルと同等の解析結果が得られます。

- コーナー条件設定の設定自由度が低い

IBISモデルの持てる条件はTyp,Min,Maxの3条件のみになります。それらの条件はPVT(プロセス・電源電圧・温度)条件が 特定の組み合わせである場合をTyp,Min,Max条件それぞれに割り当てます。例えば、プロセス条件がSS,電源電圧がworst、温度条件が高温状態のときの条件組み合わせをmin条件とするという形で定義するので、Typ,Min,Maxにそれぞれ割り当てられている条件以外の組み合わせではシミュレーションできません。

- LSI内部での遅延は再現しない

IBISモデルは基本的にICの最終段となるIOバッファの特性のみを再現したモデルなので、LSI内部での遅延やジッタなどの表現はできません。これらを表現する場合にはモデルやシミュレーションでの設定を工夫する必要があります。

IBISモデルの記述内容

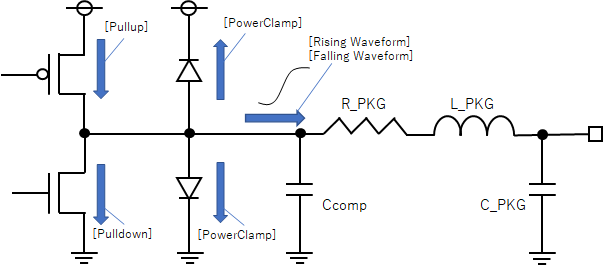

IBISモデルの構成と記述内容について説明します。IBISモデルは等価回路的に表すと下記のような構成となっており、それぞれの要素の特性が数値やテーブル形式で記述されています。

「Package」 ・・・ パッケージのRLC値

「Ccomp」 ・・・ IOの負荷容量

「Pullup」 ・・・ 電源側トランジスタのI-V特性

「Pulldown」 ・・・ GND側トランジスタのI-V特性

「PowerClamp」・・・ 電源側クランプダイオードのI-V特性

「GndClamp」 ・・・ GND側クランプダイオードのI-V特性

「Rising waveform」・・・ 出力がLow⇒Highに切り替わるときの立ち上がり特性

「Falling waveform」・・・ 出力がHigh⇒Lowに切り替わるときの立下り特性

InputバッファやOutputバッファなどのIOの種類によって、必要となる記述が異なります。

例えば、Inputバッファの場合は出力特性が必要ないので、「PowerClamp」「GND Clamp」「Ccomp」「Package」といった記述のみが使用されます。

IBISを使用可能なシミュレーションツール

最後に、代表的なIBISモデルを使用して伝送線路のシミュレーションができるツールを紹介いたします。大手EDAベンダーだと下記のツールがIBISモデルを用いた伝送線路解析に対応しています。他にも様々なツールでIBISモデルのシミュレーションに対応してますので、金額やシミュレーションの内容に応じてツールを選択するとよいかと思います。

・Synopsys HSPICE

・Mentor Hyperlynx

・Keysight ADS

・Cadence Sigrity

・ANSYS Designer

まとめ

今回はIBISモデルの基本情報について説明しました。IBISモデルはICのIOバッファの特性をモデル化したもので、SPICEモデルと比較して計算の軽さ、情報の秘匿性、取り扱いの簡単さなどで利点があります。IBISモデルを用いることで基板レイアウトの設計品質が問題ないか、事前に確認したり、不具合が起きた場合の解析などが可能となります。本記事が読者様のお役に立てれば幸いです。

コメント